在数字电路中, A二进制加减法是一种能够在一个电路本身中对二进制数进行加减的技术。执行的操作取决于控制信号保持的二进制值。它是ALU(算术逻辑单元)的组件之一。

该电路需要具备"异或门", "二进制加法和减法", "全加器"的先决知识。

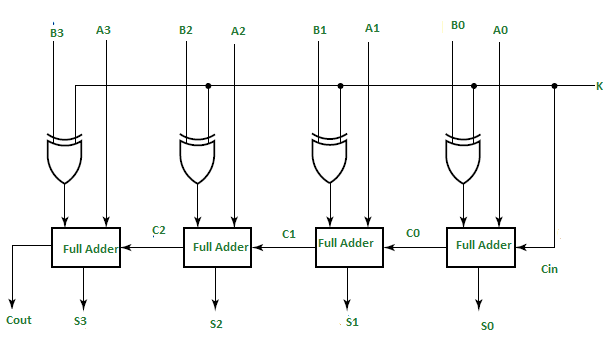

让我们将两个4位二进制数A和B视为数字电路的数字电路输入

A0 A1 A2 A3 for A

B0 B1 B2 B3 for B该电路由4个全加法器组成, 因为我们要对4位数字进行运算。控制线K保持二进制值0或1, 该二进制值确定所执行的操作是加还是减。

如图所示, 第一个全加法器直接具有控制线作为其输入(输入进位C0), 输入A0(A的最低有效位)直接输入到全加法器中。第三个输入是B0和K的异或(图中的S, 但不要将其与Sum-S混淆)。产生的两个输出是和/差(S0)和进位(C1)。

如果K(控制线)的值为1, 则B0(exor)K = B0'(补码B0)的输出。因此, 该运算将为A +(B0')。现在, 两个数字A和B的2的补数减法由A + B'给出。这表明当K = 1时, 对四个位数执行的运算是减法。

类似地, 如果K的值= 0, 则B0(外)K = B0。操作是A + B, 这是简单的二进制加法。这表明当K = 0时, 对四个位数执行的运算是相加的。

然后C0作为其输出之一串行传递到第二个全加法器。总和/差S0被记录为总和/差的最低有效位。 A1, A2, A3是第二, 第三和第四全加器的直接输入, 然后第三输入是分别与K, 第二, 第三和第四全加器相加的B1, B2, B3。进位C1, C2作为输入之一串行传递到后续的全加法器。 C3成为总和与差之和。记录S1, S2, S3以与S0形成结果。

对于n位二进制加法器-减法器, 我们使用n个完全加法器。

例子:

让我们取两个3位数字A = 010和B = 011, 并将它们与控制线的两个值一起输入到全加法器中。

For K=0:

B0(exor)K=B0 and C0=K=0

Thus from first full adder

= A0+B0

= 0+1

= 1, S0=1

C1=0

Similarly, S1=0 with C2=1

S2=1 and C2=0

Thus, A = 010 =2

B = 011 = 3

Sum = 0101 = 5

For K=1

B0(exor)K=B0' and C0=k=1

Thus

S0=1 and C1=0

Similarly

S1=1 and C2=0

S3=1 and c3=1

Thus, A = 010 = 2

B = 011 = 3

Sum(Difference) = 1111 = -1