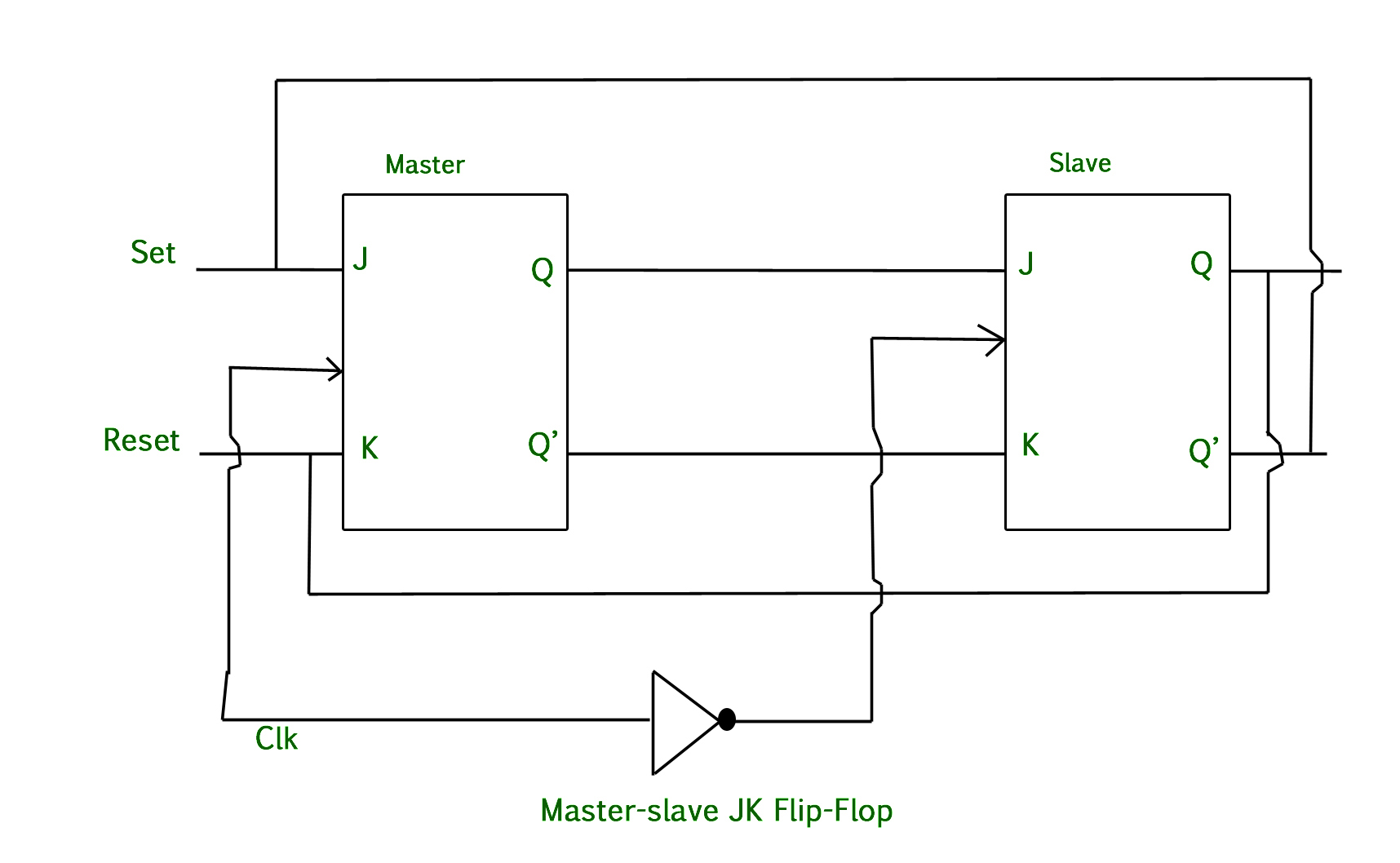

先决条件– 触发器类型及其转换

J-K触发器,如果J=K=1,如果clk=1很长一段时间,那么只要clk高,Q输出就会切换,这使得触发器的输出不稳定或不确定。这个问题在J-K触发器中称为“绕竞争”。通过确保时钟输入在很短的时间内逻辑为“1”,可以避免这个问题(绕圈竞争条件)。这介绍了主从JK触发器的概念。

主从触发器基本上是两个JK触发器串联在一起的组合。一个是“主”,另一个是“从”。主触发器的输出连接到从触发器的两个输入端,从触发器的输出反馈到主触发器的输入端。

除了这两个触发器,该电路还包括一个逆变器。逆变器连接到时钟脉冲的方式是将反向时钟脉冲给予从触发器。换句话说,如果主触发器CP=0,那么从触发器CP=1,如果主触发器CP=1,那么从触发器CP=0。

主从触发器的工作–

- 当时钟脉冲变为1时, 从机被隔离; J和K输入可能会影响系统状态。从触发器被隔离, 直到CP变为0。当CP回到0时, 信息从主触发器传递到从触发器, 并获得输出。

- 首先, 主触发器为正电平触发, 从触发器为负电平触发, 因此主控制器在从控制器之前做出响应。

- 如果J = 0和K = 1, 则主机的高Q'输出将进入从机的K输入, 并且时钟迫使从机复位, 因此从机复制了主机。

- 如果J = 1且K = 0, 则主机的高Q输出将进入从机的J输入, 并且时钟的负跳变将设置从机, 从而复制主机。

- 如果J = 1和K = 1, 则它将在时钟的正跳变上切换, 因此从机将在时钟的负跳变上切换。

- 如果J = 0和K = 0, 则禁用触发器, 并且Q保持不变。

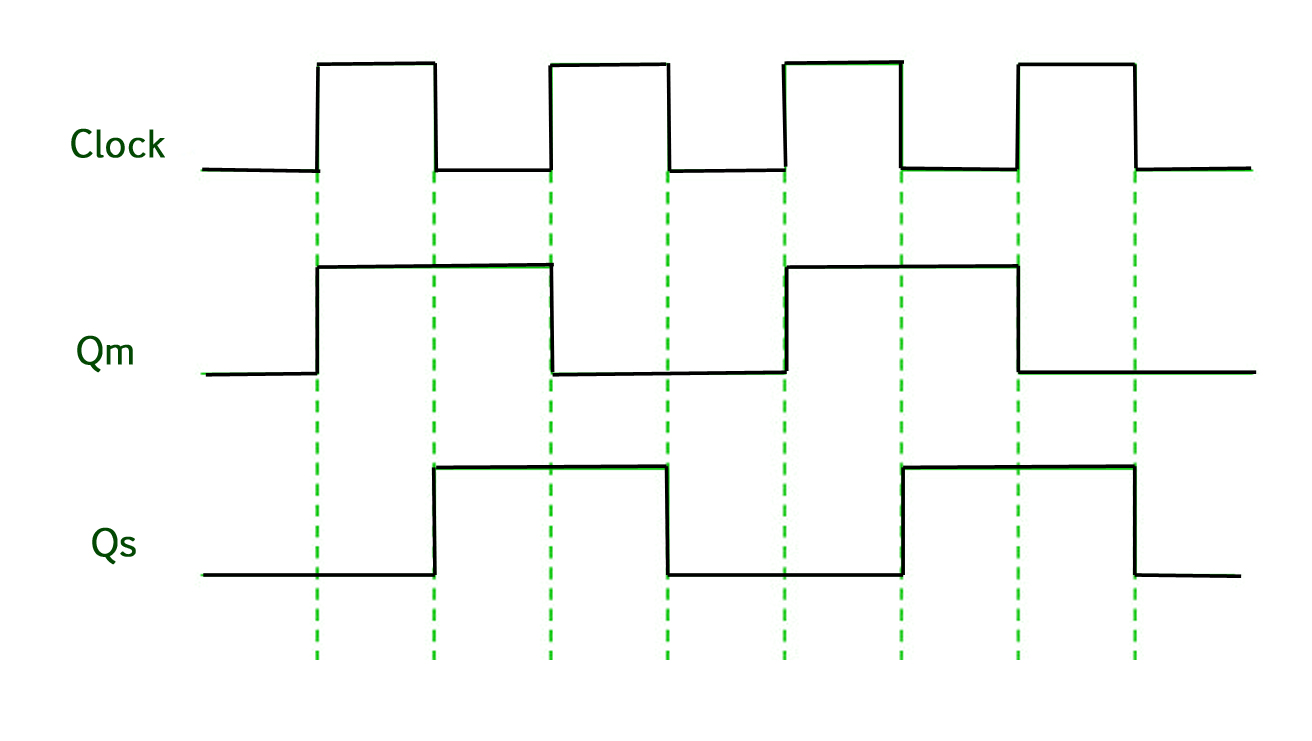

主触发器的时序图–

- 当时钟脉冲为高电平时, 主机的输出为高电平, 并保持高电平直到时钟为低电平, 因为状态已存储。

- 现在, 当时钟脉冲再次变为高电平时, 主机的输出变为低电平, 并保持低电平直到时钟再次变为高电平。

- 因此, 切换发生了一个时钟周期。

- 当时钟脉冲为高电平时, 主机可操作, 但从机不工作, 因此从机的输出保持低电平直到时钟保持高电平。

- 当时钟为低电平时, 从机开始工作并保持高电平, 直到时钟再次变为低电平。

- 由于输出每周期更改一次, 因此切换在整个过程中进行。

这使得主从J-K触发器成为同步设备, 因为它仅以时钟信号的时序传递数据。