8259微处理器定义为可编程中断控制器(PIC)微处理器。 8085和8086中分别有5个硬件中断和2个硬件中断。但是通过将8259与CPU连接, 可以提高中断处理能力。 8259将多个中断输入源组合为一个中断输出。单个PIC的接口从IR0-IR7提供8个中断输入。

例如, 8085和8259的接口将8085微处理器的中断处理能力从5个中断级别提高到8个中断级别。

8259 PIC微处理器的功能–

- 英特尔8259专为英特尔8085和英特尔8086微处理器而设计。

- 可以通过电平触发或边沿触发的中断电平进行编程。

- 我们可以屏蔽中断请求寄存器的各个位。

- 通过级联更多的8259 PIC, 我们可以将中断处理能力提高到64个中断级别。

- 不需要时钟周期。

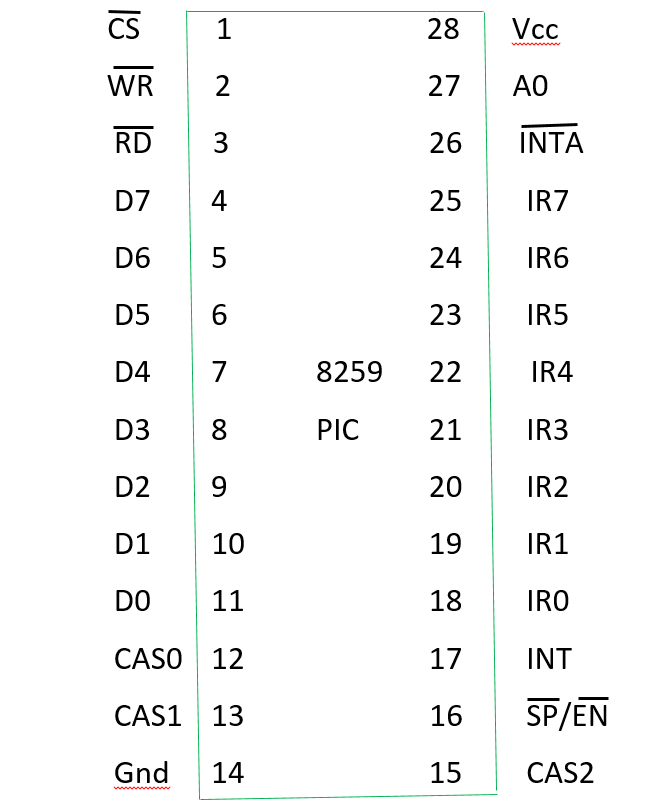

8259的引脚图–

通过上图我们可以看到8259 PIC微处理器中共有28个引脚, 其中Vcc:5V电源和Gnd:接地。其他引脚的用法说明如下。

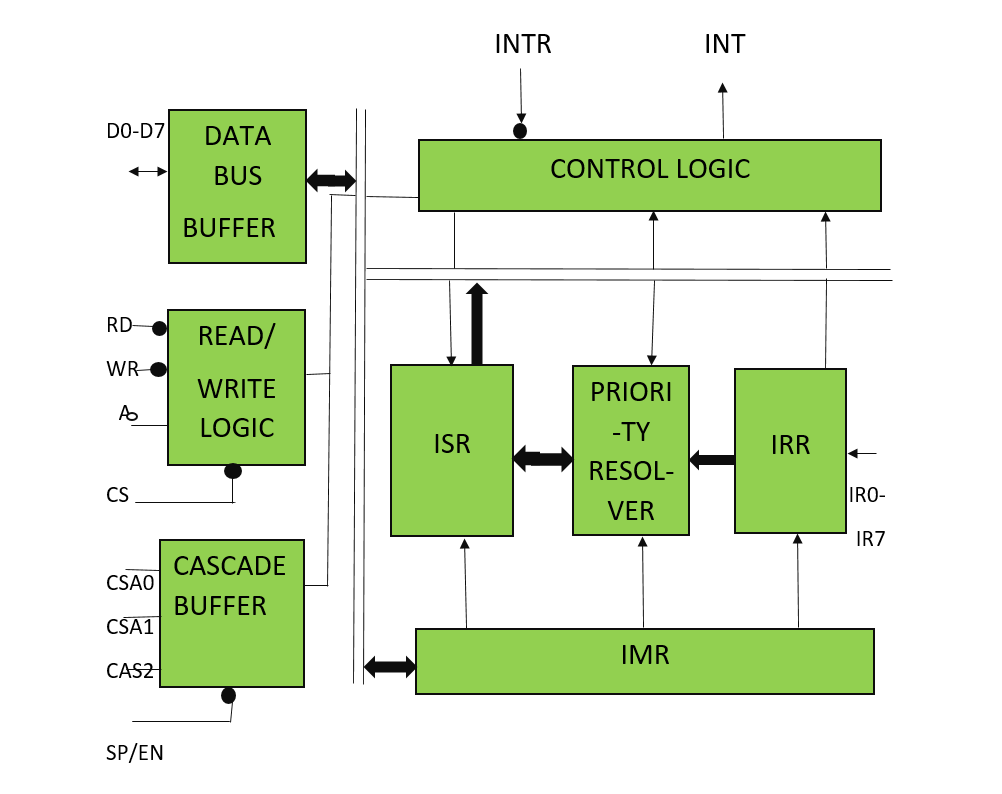

8259 PIC微处理器框图–

框图包括8个块, 分别是:数据总线缓冲区, 读/写逻辑, 级联缓冲区比较器, 控制逻辑, 优先级解析器和3个寄存器-ISR, IRR, IMR。

数据总线缓冲区–

该模块通过充当缓冲区用作8259和8085/8086微处理器之间的中介。它从8085(假设)微处理器获取控制字, 并将其传输到8259微处理器的控制逻辑。同样, 在8259微处理器选择了中断之后, 它将所选中断的操作码和中断服务子例程的地址传输到另一个连接的微处理器。数据总线缓冲器由8位组成, 在框图中表示为D0-D7。因此, 表明一次最多可以传输8位数据。

读/写逻辑–

仅当CS引脚的值为低电平时(该引脚为低电平有效), 该模块才起作用。该模块负责数据流, 具体取决于RD和WR的输入。这两个引脚是低电平有效引脚, 用于读取和写入操作。

控制逻辑–

它是微处理器的中心, 并控制每个模块的功能。它的INTR引脚与其他微处理器连接以接收中断请求, 而INT引脚则提供输出。如果启用了8259, 并且另一个微处理器的中断标志为高电平, 则这将导致输出INT引脚的值为高电平, 并且8259以这种方式响应另一个微处理器的请求。

中断请求寄存器(IRR)–

它存储所有请求中断服务的中断级别。

中断服务寄存器(ISR)–

它存储当前正在执行的中断级别。

中断屏蔽寄存器(IMR)–

它存储必须通过存储中断级别的屏蔽位来屏蔽的中断级别。

优先解决方案–

它检查所有三个寄存器并设置中断的优先级, 并根据中断的优先级在ISR寄存器中设置优先级最高的中断。同样, 它重置IRR中已经服务的中断级别。

级联缓冲区–

为了提高中断处理能力, 我们可以通过级联缓冲器进一步级联更多的引脚。因此, 在增加中断能力的过程中, CSA线用于控制多个中断结构。

SP / EN(从程序/使能缓冲器)引脚设置为高电平时, 在主机模式下工作, 在从机模式下工作。在非缓冲模式下, SP / EN引脚用于指定8259是主机还是从机, 而在缓冲模式下, SP / EN引脚用作使能数据总线的输出。